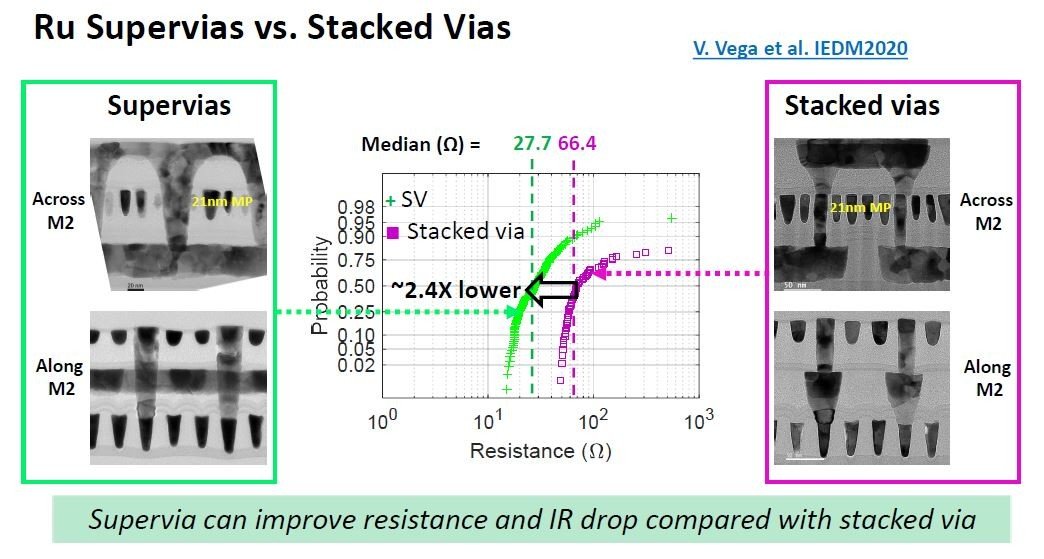

多層配線のビア抵抗を大幅に低減する「スーパービア」

スーパービア(左)と従来技術(スタックビア)(右)の抵抗値(測定値)。写真は断面の電子顕微鏡観察像。配線ピッチはM2が21nm、M1とM3が36nm。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)