高融点金属の多層配線技術が2nm以降のCMOSを実現

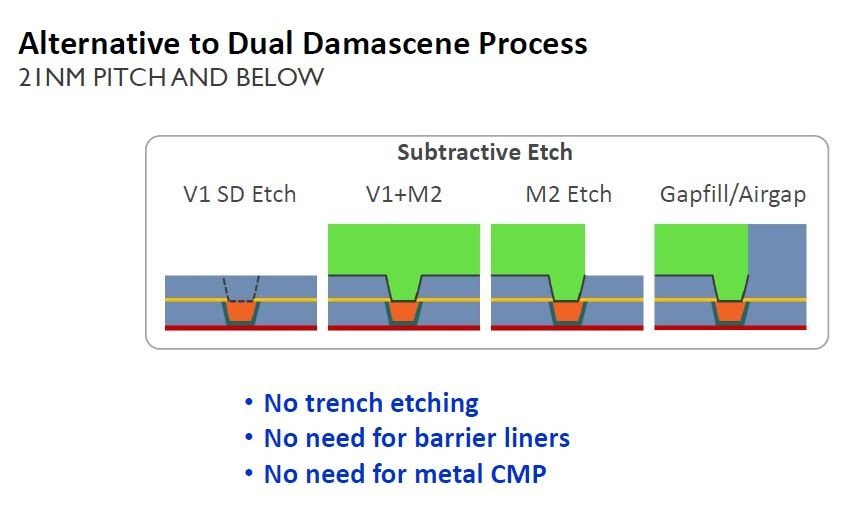

セミダマシン(Semi-Damascene)の配線形成プロセス。成膜とエッチングによって配線とビア電極を形成する。ビアの周囲は絶縁膜あるいはエアギャップとなる。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)