10nm以下の極短チャンネルを目指す2次元(2D)材料のトランジスタ

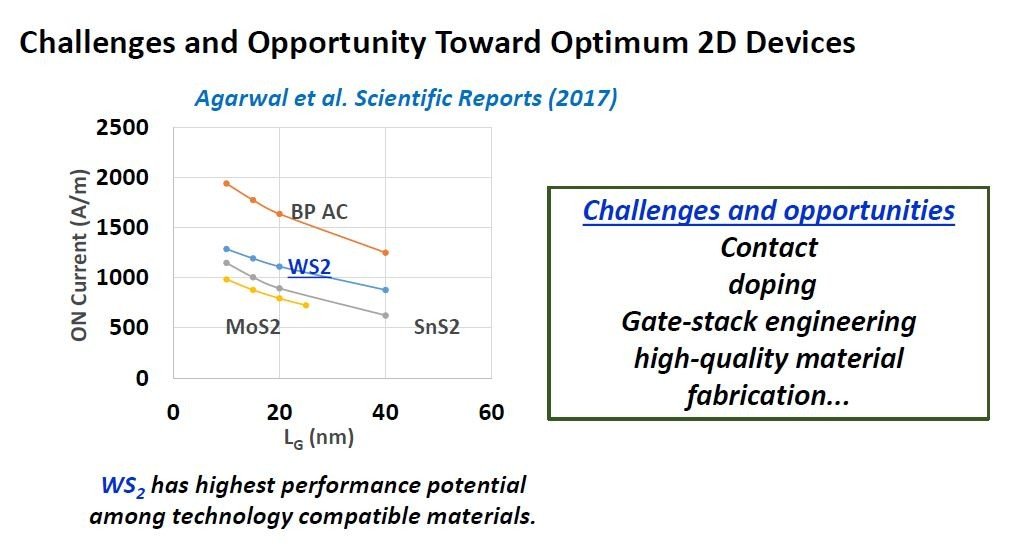

さまざまな2次元(2D)材料をチャンネルとするFETのオン電流とゲート長の比較(左)と、2D FETの課題(右)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)