10nm以下の極短チャンネルを目指す2次元(2D)材料のトランジスタ

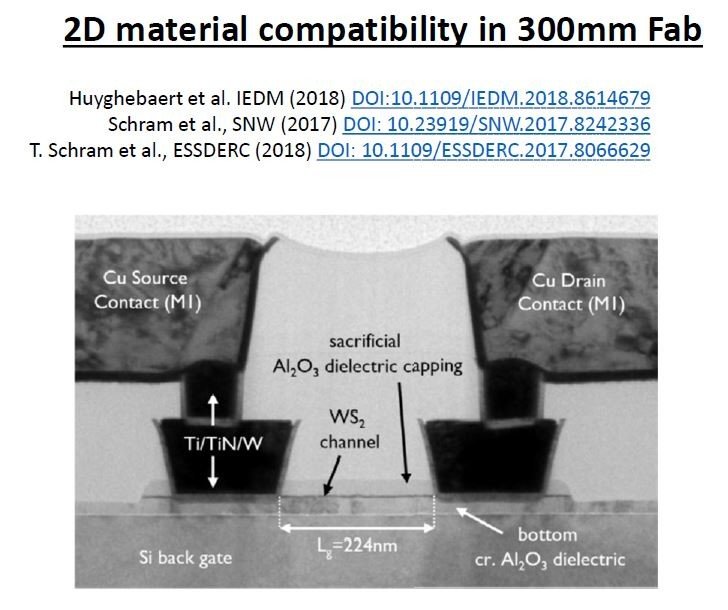

試作した2次元(2D)材料トランジスタの断面を電子顕微鏡で観察した画像。チャンネル(中央下)の材料は二流化タングステン(WS2)。チャンネルの下がアルミナのゲート絶縁膜、その下がシリコンのバックゲート。チャンネルのゲート長は224nm。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)