10nm以下の極短チャンネルを目指す2次元(2D)材料のトランジスタ

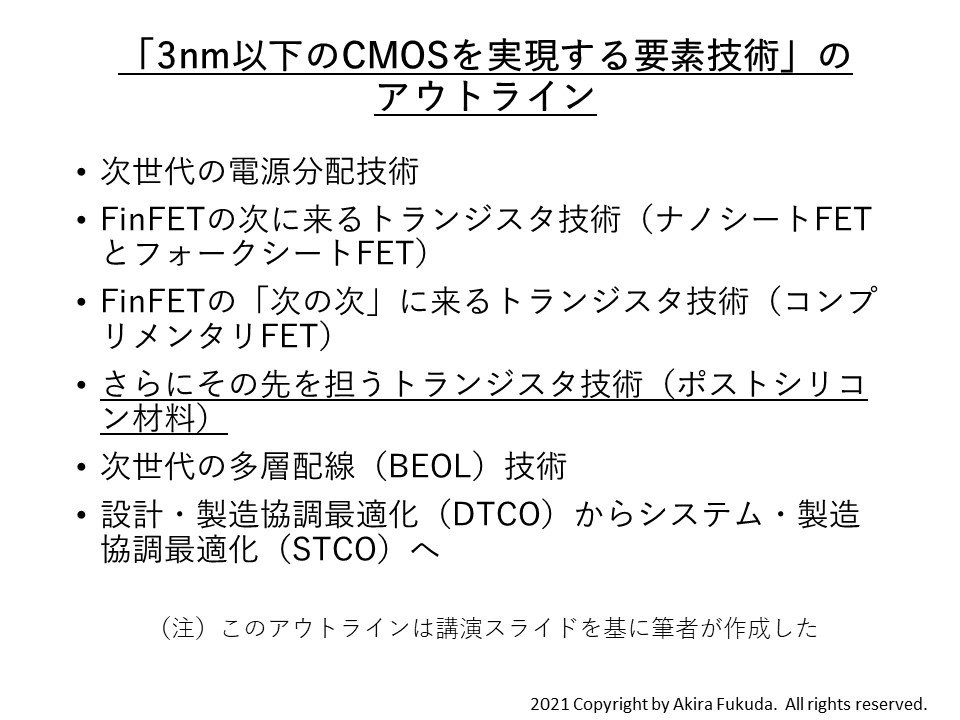

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前回から、「さらにその先を担うトランジスタ技術(ポストシリコン材料)」の講演パートを紹介している(クリックで拡大)