次々世代のトランジスタ「シーケンシャルCFET」でシリコンの限界を突破(後編)

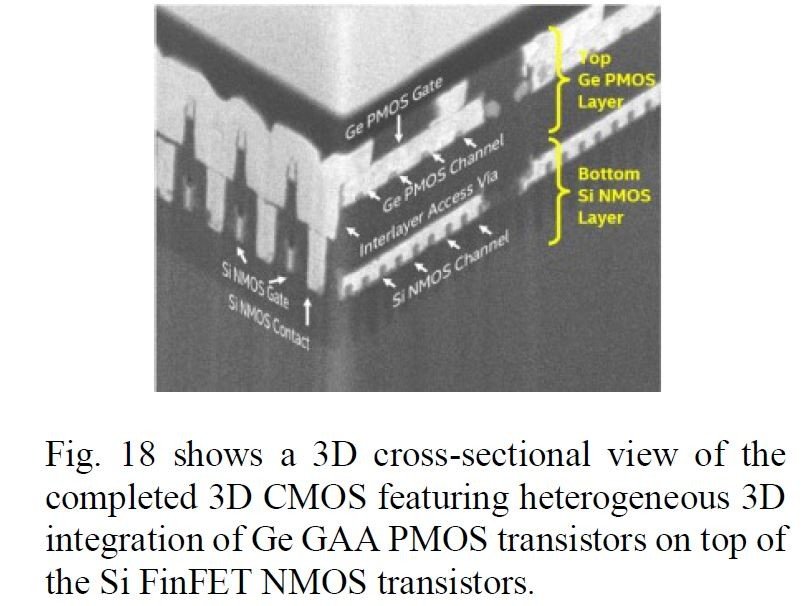

300mmウエハーによって試作したシーケンシャルCFET(3次元CMOS)の断面を電子顕微鏡で観察した画像。左側はゲート電極の断面。右側はチャンネルの断面。出典:intelが2019年12月に国際学会IEDMで発表した論文「300mm Heterogeneous 3D Integration of Record Performance Layer Transfer Germanium PMOS With Silicon NMOS For Low Power High Performance Logic Applications」(論文番号29.7)から(クリックで拡大)