次々世代のトランジスタ「シーケンシャルCFET」でシリコンの限界を突破(前編)

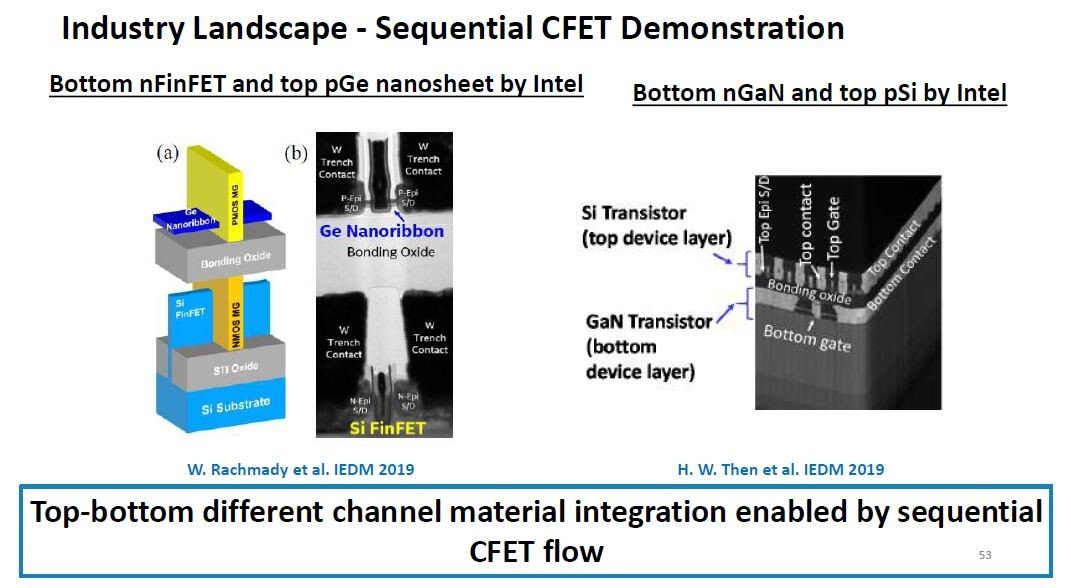

シリコン(Si)のトランジスタと、別の材料によるトランジスタを組み合わせたコンプリメンタリFET(C(Complementary)FET)の試作例。左はボトム側にnチャンネルのSi FinFET、トップ側にpチャンネルのゲルマニウム(Ge)ナノリボン(ナノシート)構造を選択したCFET。右はボトム側にnチャンネルのSi MOSFET、トップ側にpチャンネルの窒化ガリウム(GaN) MOSFETを選択したCFET。いずれもintelが試作して国際学会IEDM(IEDM 2019)で発表したもの。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)