次々世代のトランジスタ「シーケンシャルCFET」が抱える、もう1つの課題

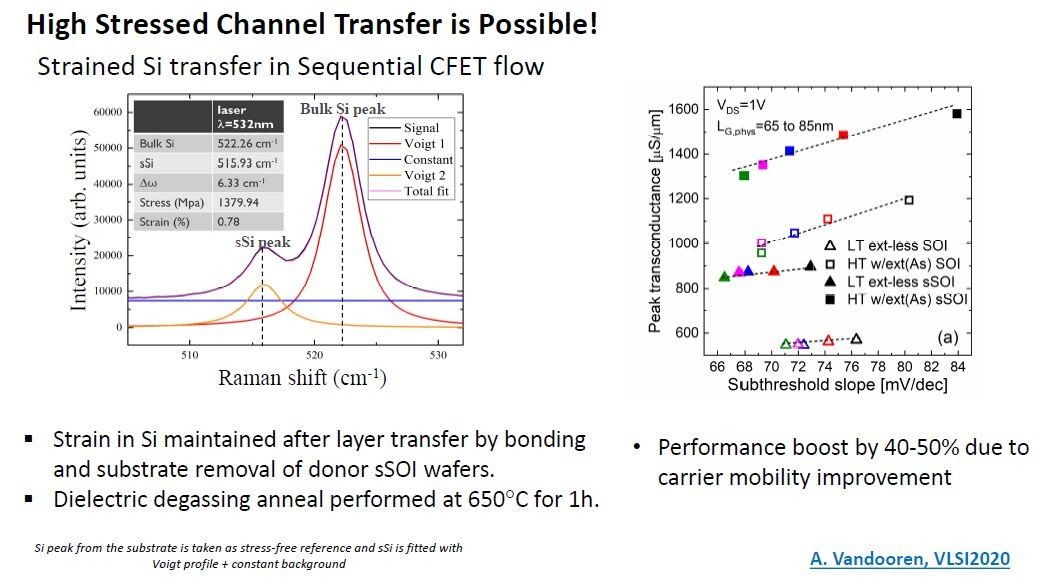

歪みシリコンSOI(sSOI)によるトランジスタの性能向上。左はウエハー貼り合わせ工程の脱ガス熱処理(650℃、1時間)を加えても歪みシリコンが維持されていることを示す分析結果(ラマン散乱分光分析)。右はnチャンネルMOSトランジスタのサブスレッショルドスロープ(SS)(横軸)とトランスコンダクタンス(ピーク値)の関係。LTは低温プロセス、HTは高温プロセス、extはエクステンション(「ext-less」はエクステンションなし、「w/ext(As)」はヒ素(As)を注入することによるエクステンションの形成を意味する)、SOIは通常のシリコンチャンネル、sSOIは歪みシリコンチャンネルを指す 出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond – device architectures, parasitics and materials」の配布資料)