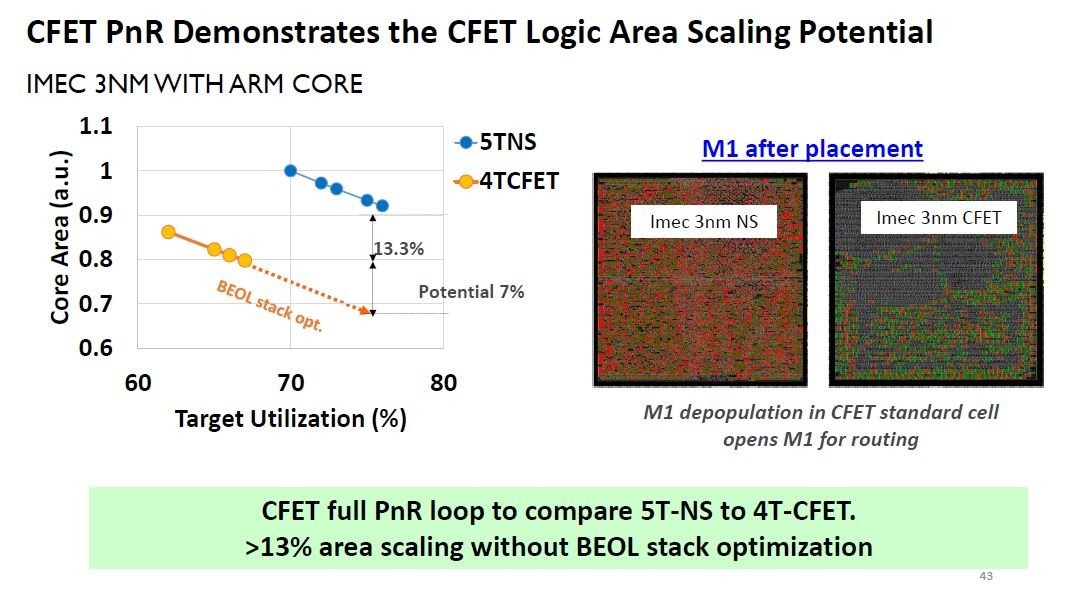

コンプリメンタリFET(CFET)でCMOS基本セルの高さを半分に減らす

Armプロセッサコアのシリコン面積の比較(相対値)。5Tのナノシート構造に比べて4TのCFETはコアの面積が13.3%減少する(左)。またCFETは第1層金属配線(M1)のルーティングに余裕ができる(右)ので、金属配線工程(BEOL)の最適化によってコア面積をさらに減らせる。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)(クリックで拡大)