論理回路セルとSRAMセルを縮小するフォークシート構造

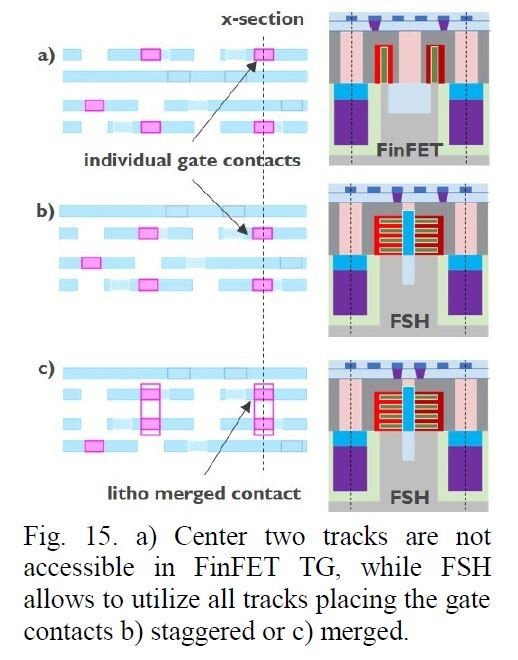

CMOS基本セル(インバーター)のレイアウトとゲートコンタクトのレイアウト。上(a)はトランジスタがFinFETの場合。水平方向の4本のトラックで中央の2本にはゲートコンタクトをレイアウトできない。中央(b)と下(c)はトランジスタがフォークシート構造の場合。全てのトラックにゲートコンタクトをレイアウトできる。出典:2019年12月にIEDM2019でimecが発表した論文「Novel forksheet device architecture as ultimate logic scaling device towards 2nm」(論文番号36.5)から(クリックで拡大)