フォークシート構造のCMOSロジック製造プロセス

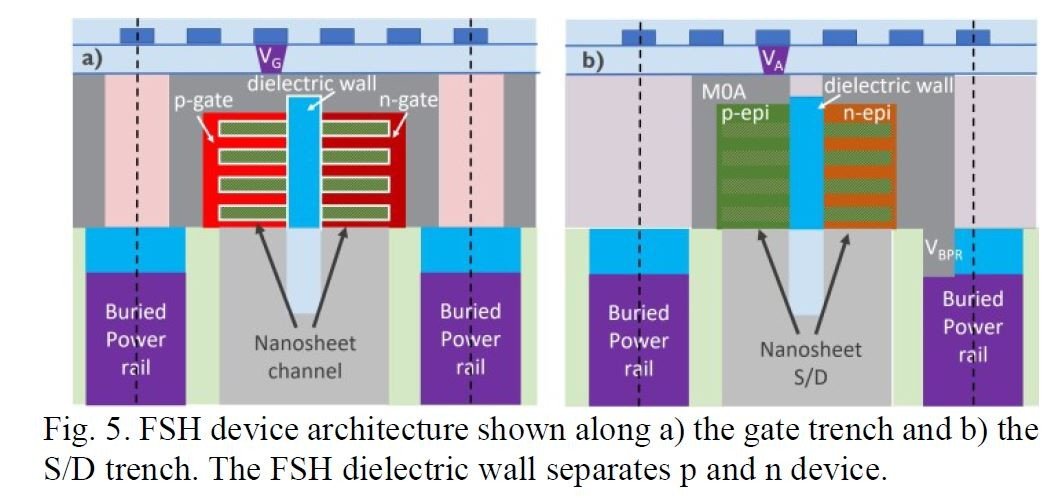

フォークシート(FSH)構造のCMOSロジックを構成するトランジスタ対の断面構造図。左の構造図(a)はゲート電極での断面。トランジスタ対の左がpチャンネル、右がnチャンネル。右の構造図(b)はアクティブ領域(ソース/ドレイン領域)での断面。いずれも絶縁膜の壁がトランジスタ対を電気的および物理的に分離している。出典:2019年12月にIEDM2019でimecが発表した論文「Novel forksheet device architecture as ultimate logic scaling device towards 2nm」(論文番号36.5)から(クリックで拡大)