電源供給配線網(PDN)をシリコンダイの裏面に配置して電源をさらに安定化

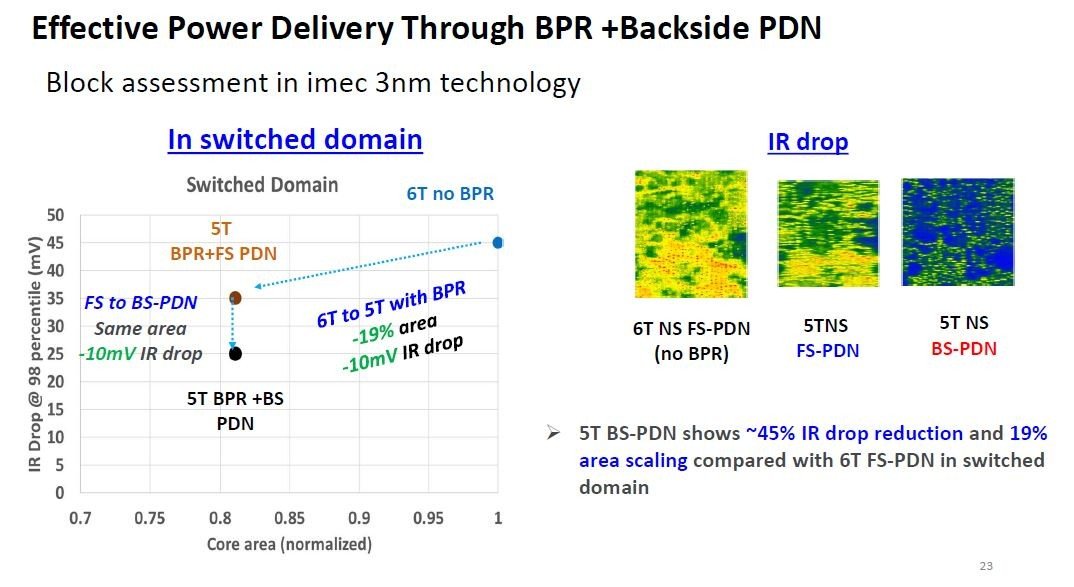

BPRとBS-PDNの効果。左は回路ブロック(コア)の面積と電源電圧降下の関係。右は回路ブロックの温度分布(IRドロップの大きさを反映)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)