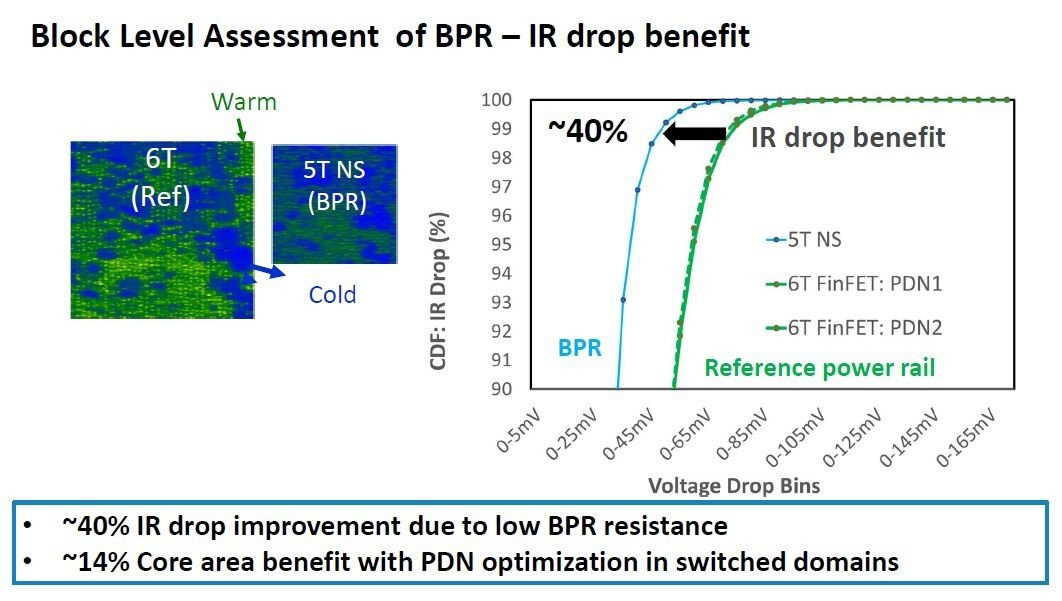

電源/接地線の埋め込みで回路ブロックの電圧降下を半分以下に低減

回路ブロックでBPRの効果を検証した結果。左は回路ブロックの大きさと温度分布の比較。BPRを採用した5T(5トラック)セルの回路ブロックでは、温度の高い部分(Warm)がやや小さくなっている。右は電圧降下(IRドロップ)の累積分布を比較したグラフ。BPRを導入した5Tセルの回路ブロックでは、電圧降下を約40%減と大幅に低くできた。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)