電源/接地線の埋め込みで回路ブロックの電圧降下を半分以下に低減

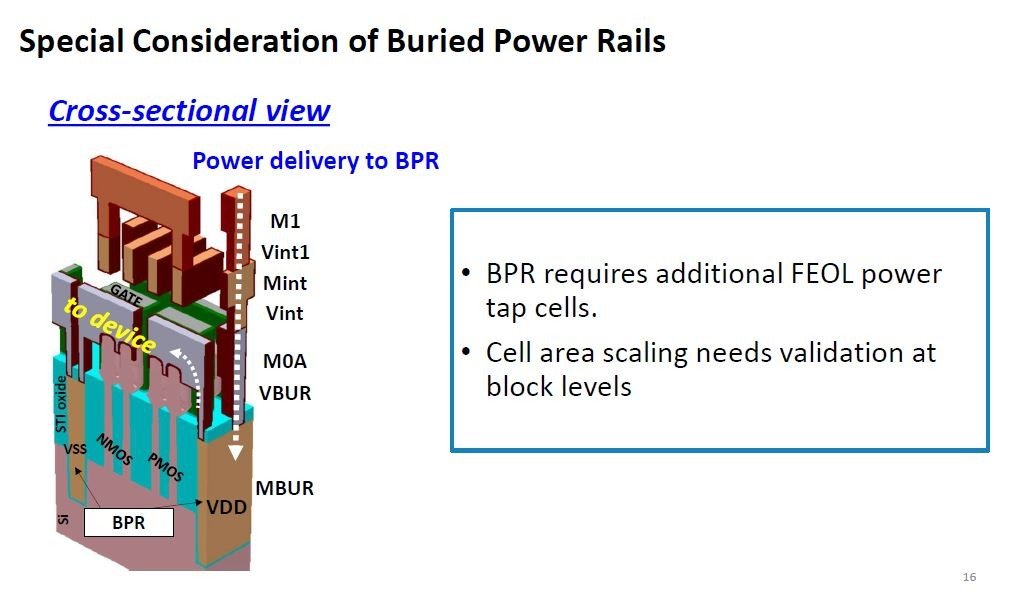

電源/接地配線を基板側に埋め込む技術(BPR:Buried Power Rails)を採用したCMOSロジック基本セルの断面構造。BPRに電源を供給する構造(白い矢印の部分)が必要となる。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)