CMOSロジックの高密度化を後押しする次世代の電源配線技術

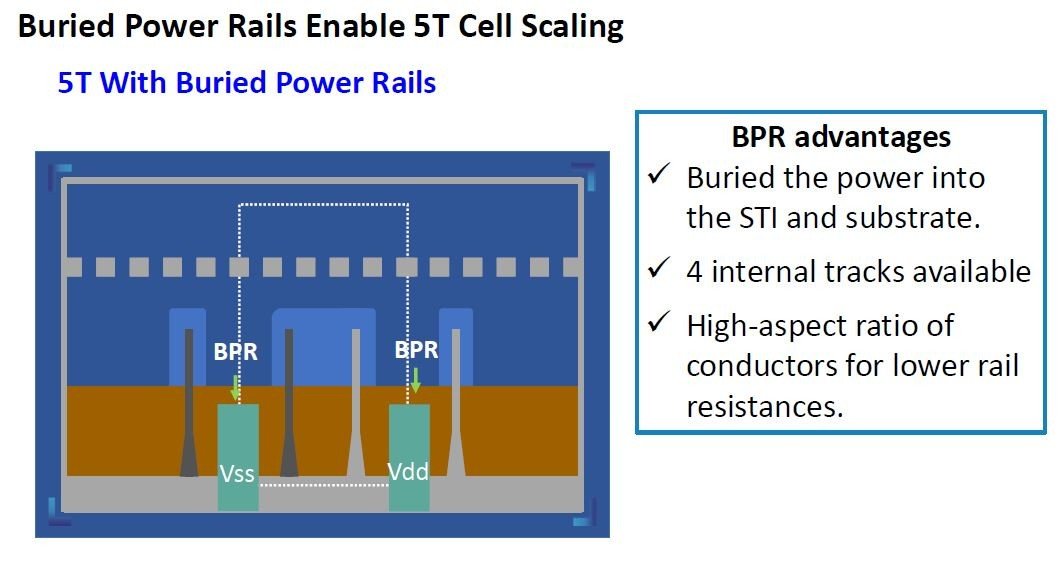

セルの高さを5トラック(5T)に下げたCMOSロジック基本セルの断面構造図(FinFETのフィンおよび最下層金属配線と直交する方向の断面)。電源配線と接地配線を基板側に埋め込む(BPR)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)