CMOSロジックの高密度化を後押しする次世代の電源配線技術

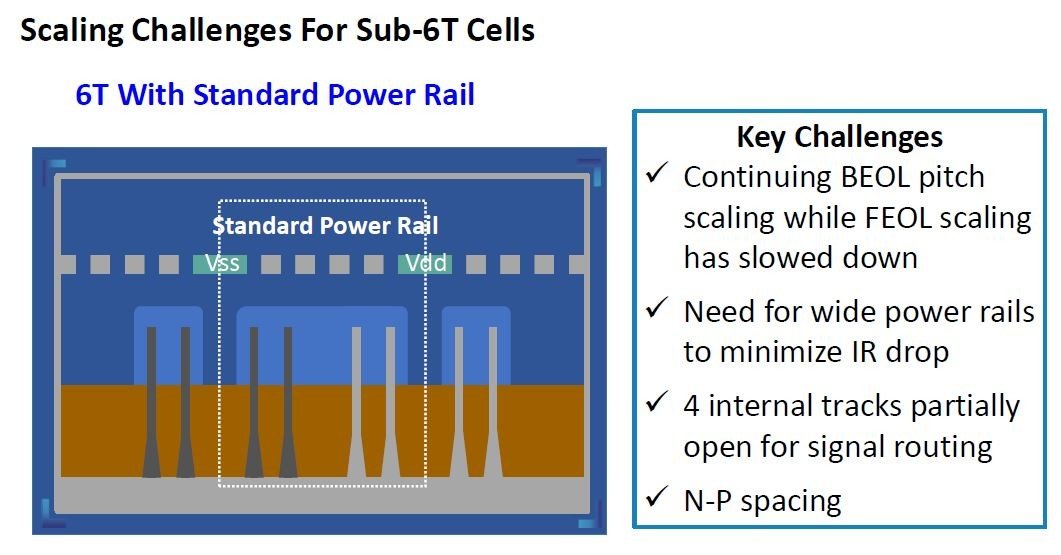

CMOSロジック基本セルの断面構造図(FinFETのフィンおよび最下層金属配線と直交する方向の断面)。セルの高さは6トラック(6T)である。CMOSロジックの密度をさらに高めるためにトラック数を減らそうとすると、いくつもの課題が立ちふさがる。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)