AIプロセッサを開発した東芝メモリの狙い

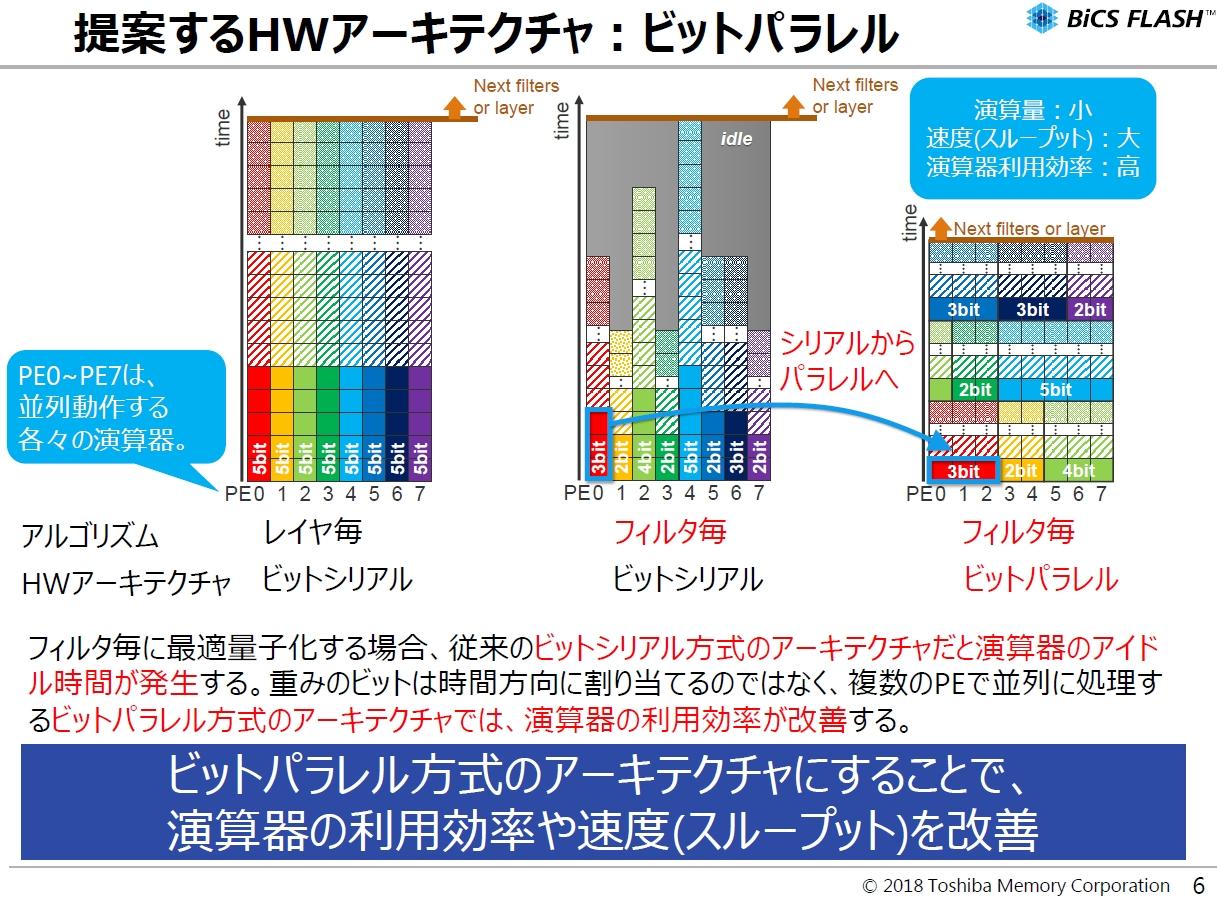

「ビットパラレル方式」のアーキテクチャ。左=従来のビットシリアル方式は、各演算器(PE:Processing Element)において時間軸方向(縦軸方向)に1ビットずつ積み上げていくようなイメージ/中央=フィルターごとの最適量子化を、ビットシリアル方式に適用させると、1個当たりで演算するビット数は減るものの、全体としてみると利用効率がよくない/右=ビットパラレル方式は、1ビットずつに分解し、各PEに順番に割り当てていく。「テトリス」のように、PEが休むひまなく演算するよう、隙間を埋めていくようなイメージだ 出典:東芝メモリ(クリックで拡大)