「このデモは世界初」、ザイリンクスが次期FPGAの28Gbps波形を披露

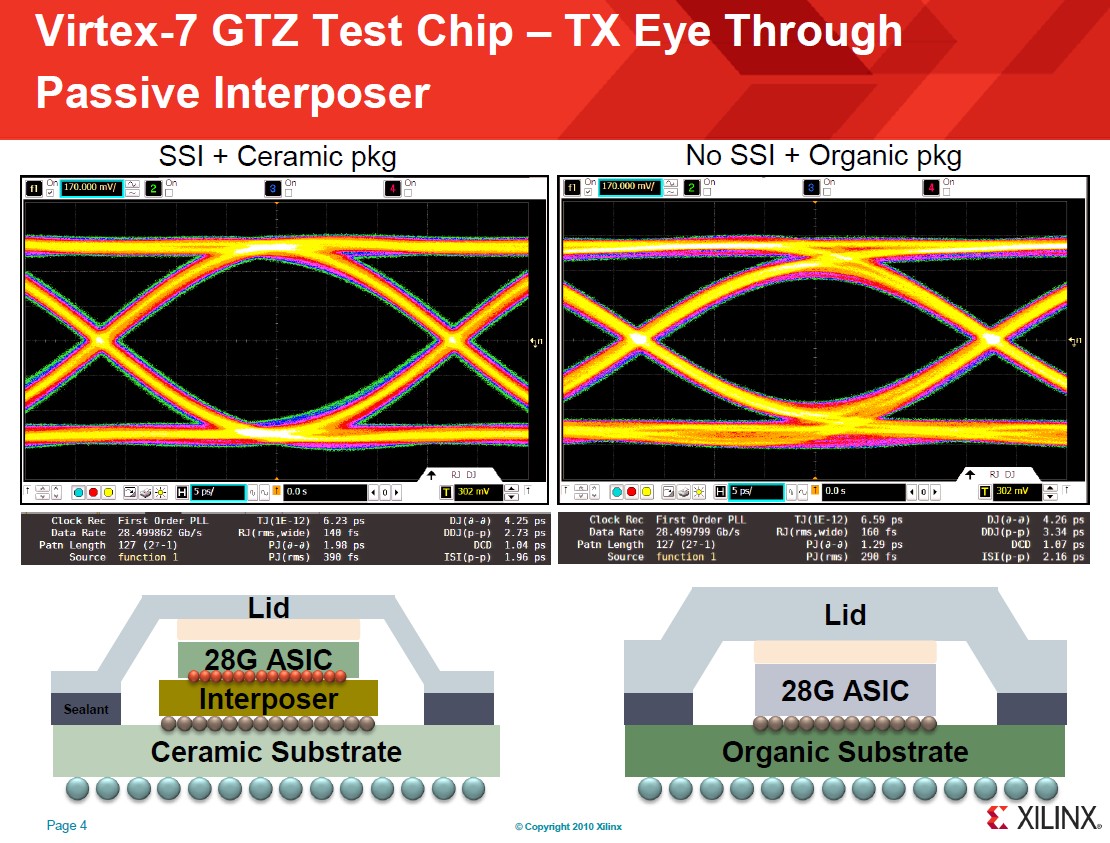

デモの横で見せていたプレゼンテーションスライド。左側は今回のデモ、右側は従来のデモで用いていたパッケージ内の構成である。今回のデモでは、パッケージの底部の基板(Substrate)と28Gビット/秒SERDESの間に、シリコンインターポーザが挿入された。それにもかかわらず、データ伝送波形の品質は従来の構成と同等以上を維持している。「スタックド シリコン インターコネクトを導入しても、シグナルインテグリティが低下しないことを示す結果だ」(XilinxのSystem IO Specialist FAEであるOusama Hage氏)と説明した。出典:ザイリンクス(クリックで拡大)